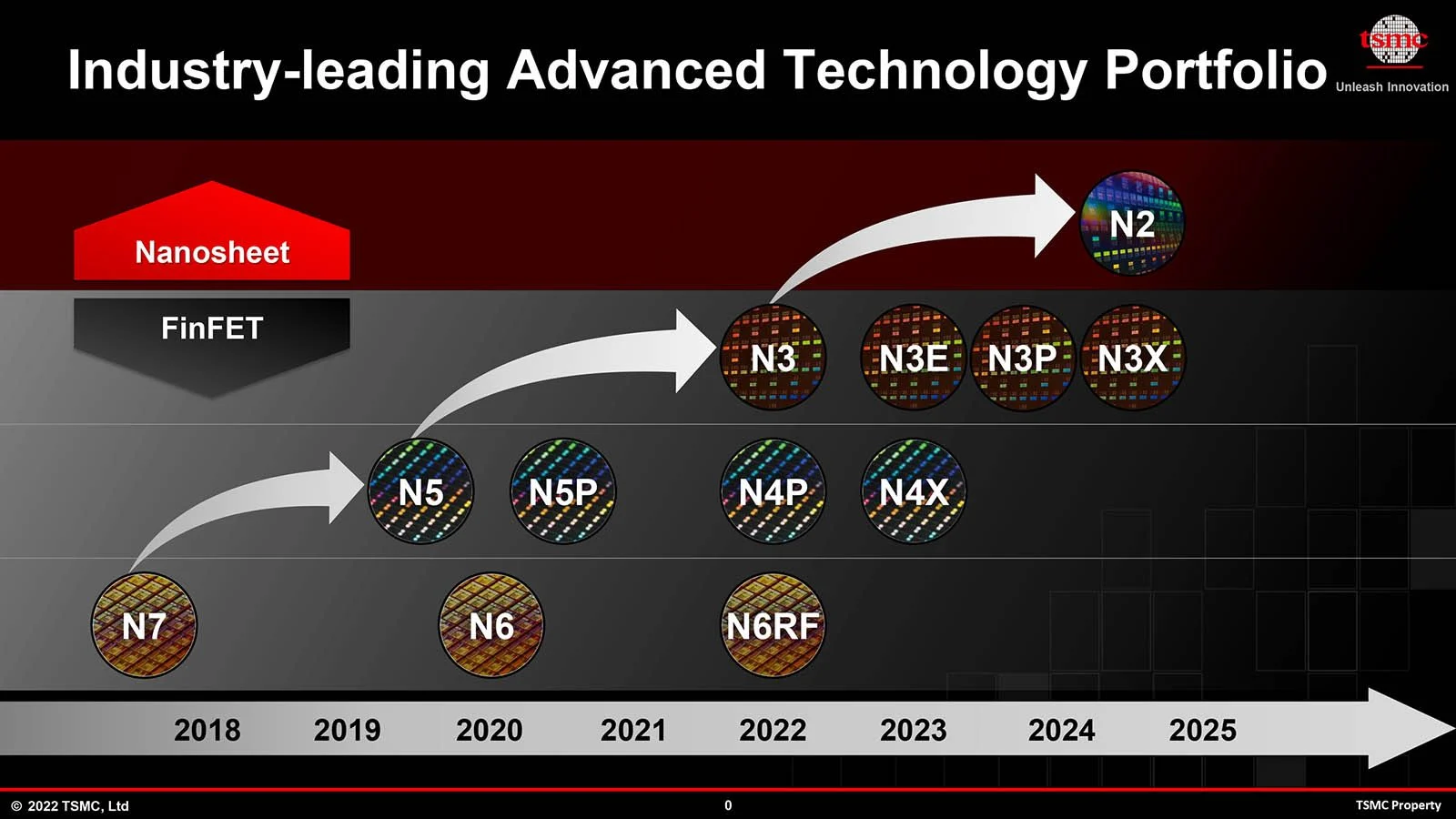

芯片冠军台积电计划于 2025 年实现 2nm 刻蚀,这是半导体领域疯狂竞赛中的重要一步。虽然几年前我们还几乎没有希望达到 5 纳米,但我们不仅已经在 2022 年进行了 4 纳米雕刻,另外3nm的路线图已经完成2nm正在准备产业化。

来自台湾台积电的名为 N2 的 2 nm 技术不仅带来了预期的能耗改善和性能提升,而且最重要的是带来了下一个十年的新晶体管架构。

更节能(但功率适度增加)

2 nm 雕刻并没有大幅增加晶体管密度(与 2 nm (N3E) 相比增加 10%),而是降低了能耗。剧烈:同等性能下,下降幅度将在 25% 到 30% 之间波动。这显然是个好消息,特别是对于智能手机和所有嵌入式芯片而言。

相反,与 NE3 相比,这个过程可以让你获得力量……但没有你想象的那么多。是的,从纸面上看,从 3 纳米到 2 纳米似乎电路尺寸减少了 33%。或者节省接近 25-30% 的能源。但 N2 并没有增加 33% 的晶体管。因为处理器不仅由所谓的“逻辑”部分组成,还包含内存和模拟元件。

而这两个元件(SRAM和与电流控制相关的模拟元件)不再像过去那样减少。台积电在此展示了一个芯片示例,该芯片包含 50% 的逻辑部分(唯一充分利用晶体管尺寸缩小的优势),同时还包含 30% 的 SRAM 存储器和 20% 的模拟元件。

事实上,台积电预计晶体管密度仅比 3 nm 多 10%。那么到底如何才能实现25-30%的消耗减少呢?感谢新型晶体管。

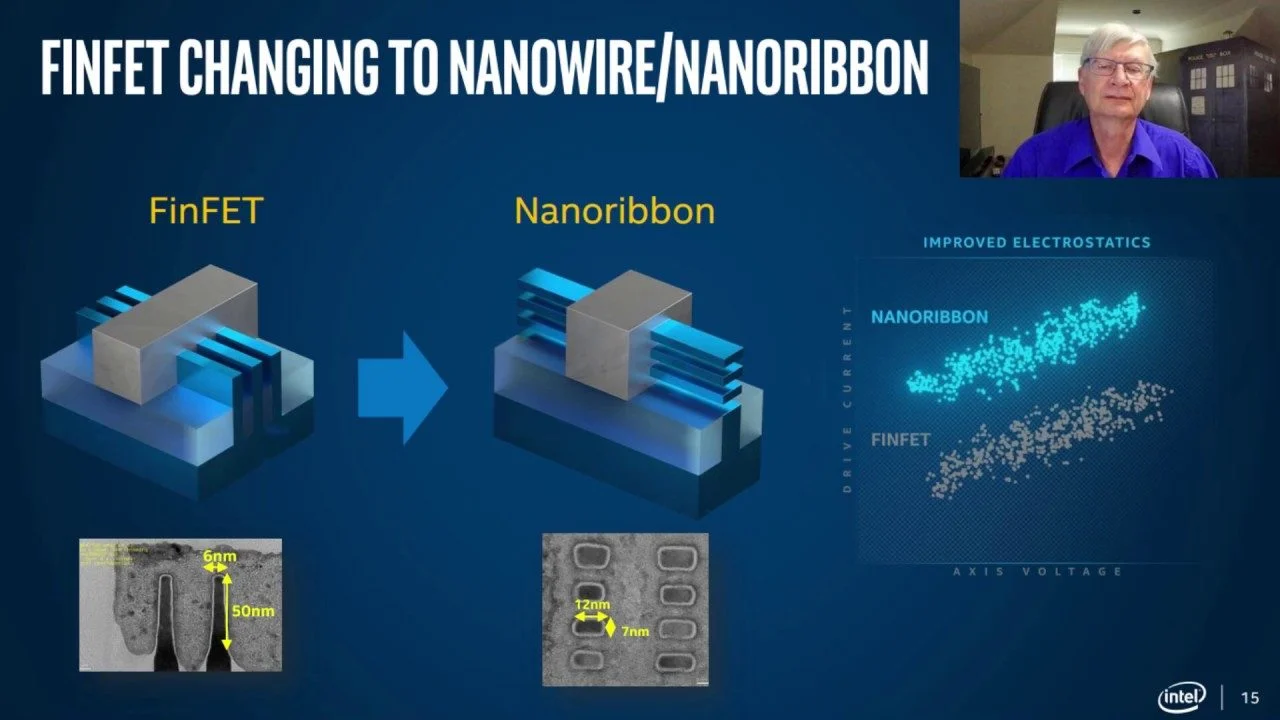

再见 FinFET,你好 GAAFET

正如我们已经告诉过你的,台积电成功地让“经典”FinFET 晶体管存活了很长一段时间。但这种鳍式晶体管结构(“fin”在英语中的意思是鳍、鳍)已经过时,另一种类型的晶体管将取而代之。台积电称为nanosheet,英特尔称为nanoribbon,最能说明问题的是三星的GAAFET名称。因为它清楚地解释了这些“纳米层/纳米线”穿过完全包围它们的逻辑门 –周围栅极场效应晶体管。

正是这种结构的本质,使电路之间更好地隔离,从而可以限制能耗。电路被完全包围的事实使得可以更好地管理能量泄漏,在电压方面有更大的自由度等。东芝于 1988 年提出的这一工艺的唯一困难是工业化。而台积电似乎是第一个为其未来客户带来好处的人——谁谈论过苹果?

来源 : 安南德科技