โปรเซสเซอร์รุ่นที่ 13 ของ Intel ซึ่งได้รับการออกแบบส่วนใหญ่ในอิสราเอล ถือเป็นชิปที่ต่างกันรุ่นที่สองของ Intel เราได้พูดคุยกับวิศวกรบางคนที่มีส่วนร่วมในการพัฒนาซึ่งอธิบายทางเลือกของพวกเขาให้เราฟัง

การเกิดกินเวลาสามปี และทารกก็พบชื่อการต่อสู้: "Raptor Lake" หรือโปรเซสเซอร์ Core 13 กระแสหลักจรุ่นของอินเทล ชิปที่ยึดถือปรัชญาของ Alder Lake รุ่นก่อนหน้า: การรวมแกนหลักขนาดใหญ่ที่มีประสิทธิภาพสูง (P-Cores) เข้ากับแกน CPU ที่เล็กกว่า แต่ประหยัดพลังงานมากกว่า (E-Cores) -ความท้าทายของ Alder Lake ซึ่งอาจหนีรอดจากนักวิจารณ์บางคนได้ ไม่ใช่แค่สถาปัตยกรรมแบบผสมผสานเท่านั้น แต่เหนือสิ่งอื่นใดได้รับการออกแบบมาให้มีจำหน่ายใน 16 รุ่นสำหรับแล็ปท็อปและเดสก์ท็อปพีซีตั้งแต่ 9 W ถึง 125 W"Isic Silas รองประธานกลุ่ม Client Computing ของ Intel ซึ่งประจำอยู่ในอิสราเอลกล่าว เขาพูดพริบตา “ว่าสำนักงานใหญ่ไม่ร้อนมากในช่วงแรกและต้องเดินทางไปอเมริกาเพื่อโน้มน้าวทีมผู้บริหาร!-

Isic Silas เป็นหัวหน้าทีมอิสราเอล ไม่เพียงแต่ดูแลการพัฒนา P-Cores ที่ผลิตในท้องถิ่นเท่านั้น แต่ยังรวมไปถึงการบูรณาการองค์ประกอบทั้งหมดของ SoC นี้ด้วย ทำให้คนรุ่นนี้ประสบความสำเร็จครั้งใหม่ทำในอิสราเอลของอินเทลและยังเป็นความภาคภูมิใจของนายสิลาสอีกด้วย”ด้วยสถาปัตยกรรมที่ได้รับการปรับปรุง เราจึงสามารถผลิตชิปขนาด 10 นาโนเมตรที่เหนือกว่าในด้านพลังงานดิบไปจนถึงชิปขนาด 5 นาโนเมตร-สามารถเข้าถึง 6 GHz, Raptor Lakeไม่ใช่สถาปัตยกรรมใหม่ แต่เป็นการปรับปรุงเชิงลึกของสถาปัตยกรรมที่มีอยู่

การเพิ่มขึ้น 15% จากรุ่นสู่รุ่นในทุกระดับ ได้แก่ การเพิ่มความถี่ การปรับปรุงการบริโภคและอัตราส่วนประสิทธิภาพ/วัตต์ การเพิ่มไมโครคอนโทรลเลอร์ใหม่ การทำงานเกี่ยวกับเฟิร์มแวร์การใช้อัลกอริธึมที่ได้รับการฝึกโดยการเรียนรู้ของเครื่อง (การเรียนรู้ของเครื่อง) เพื่อปรับปรุงการโหลดคำสั่งล่วงหน้าและพฤติกรรมการใช้งาน ฯลฯ ทั้งหมดนี้ท่ามกลางฉากหลังของโควิด ซึ่งส่งผลกระทบต่อการพัฒนาของทะเลสาบออลเดอร์ไปแล้ว ได้รับผลกระทบแต่ไม่ช้าลง: “ในช่วงเริ่มต้นของการแพร่ระบาดในเดือนกุมภาพันธ์ 2020 เราได้เปลี่ยนห้องประชุม 7 ห้องให้เป็นห้องปฏิบัติการทางเทคนิคที่ใช้งานได้ภายในเวลาเพียงไม่กี่วันเพื่อที่จะเปิดดำเนินการต่อไป โดยไม่ต้องเสี่ยงกับพนักงานของเรา-

จำนวนแกน "ใหญ่" ที่เหมาะสมที่สุด

เมื่อคุณอ่านเอกสารทางเทคนิคของโปรเซสเซอร์ Raptor Lake ที่ประกาศไปแล้ว องค์ประกอบหนึ่งที่โดนใจคุณ: หากจำนวนคอร์เพิ่มขึ้น นั่นเป็นเพราะ Intel ได้ไปไกลถึงสองเท่าของจำนวนคอร์ประสิทธิภาพต่ำ โดยไม่ต้องเพิ่มคอร์ประสิทธิภาพสูงแม้แต่ตัวเดียว

-เราทำงานในส่วนแบ่งพลังงานของชิปของเราเป็นหลัก» อธิบาย Ran Berenson และ Arik Gihon ซึ่งเป็น "สมอง" ทั้งสองที่อยู่เบื้องหลังการพัฒนาชิป -หนึ่งในความแตกต่างที่สำคัญระหว่าง 12จและวันที่ 13จรุ่นที่เราภาคภูมิใจคือส่วนอาหาร» อธิบายวิศวกรสองคน -สำหรับการใช้พลังงานเท่าเดิม แกนจะพัฒนาพลังงานมากขึ้น» พวกเขาแสดงความยินดีกับตัวเอง "ลกุญแจสำคัญในความก้าวหน้านี้คือการปรับปรุงพลังงานที่ใช้โดยการประมวลผลคำสั่งแต่ละครั้ง และเมื่อเราดูรายละเอียด เราจะเห็นว่าแอปพลิเคชันที่ดีส่วนใหญ่ใช้เธรดประสิทธิภาพสูงเพียงสองหรือสี่เธรดเท่านั้น และแอปพลิเคชันที่ใช้เธรดจำนวนมากไม่จำเป็นต้องมีความถี่สูงมาก» ดำเนินการต่อผู้เชี่ยวชาญทั้งสอง

อ่านด้วย- Core รุ่นที่ 13 Raptor Lake: Intel ต้องการฟื้นมงกุฎในฐานะราชาแห่งพีซีอย่างไร(กันยายน 2565)

เราสามารถชี้ให้เห็นได้ที่นี่ว่าแนวทางของ Intel และ AMD แตกต่างกันโดยเฉพาะเนื่องจากขนาดคอร์ที่แตกต่างกันมาก P-Cores ประสิทธิภาพสูงของ Intel นั้นใหญ่มาก, Core ของ AMD นั้นมีขนาดกลางทั้งหมด, E-core ของ Intel นั้นเล็กมาก ที่นี่แต่ละแนวทางมีจุดแข็งและจุดอ่อน หาก AMD สามารถปรับใช้คอร์ที่ "ใหญ่" มากกว่า Intel ได้ คอร์ที่กินไฟต่ำของ Intel ก็จะทำให้โปรเซสเซอร์สามารถประกอบชิปได้มากขึ้น โดยมีคอร์ที่แตกต่างกันสองคอร์ เพียงแต่ต้องผสมแกนตามกำลังเป้าหมายและการใช้พลังงาน

x86 ไม่ใช่จุดอ่อนและฟีดจากสถาปัตยกรรมอื่นๆ

ทุกปีเราอ่านเจอว่า ARM คืออนาคต และ x86 นั้นตายไปแล้ว เห็นได้ชัดว่า Intel และ AMD ไม่สามารถเห็นด้วยกับเรื่องนี้ได้ แต่ครั้งหนึ่งเราสามารถเข้าถึงวิศวกรที่อยู่เบื้องหลังสถาปัตยกรรมไมโครได้ พวกเขาสามารถตอบเราเกี่ยวกับผลกระทบเชิงลบที่ x86 และองค์ประกอบความเข้ากันได้แบบย้อนหลังจะมีต่อประสิทธิภาพการทำงาน -เราถามคำถามกับตัวเองในทุกเจเนอเรชั่น» ตอบอย่างใจเย็น Adi Yoaz ผู้อำนวยการฝ่ายสถาปัตยกรรมหลัก -มันเป็นเรื่องของกำลังต่อพื้นที่ชิป คำถามก็คือ ความเข้ากันได้นี้ส่งผลเสียต่อเรามากน้อยเพียงใด? เราต้อง 'จ่าย' เท่าไหร่เพื่อสิ่งนี้? ตามการประมาณการของเรา อาจมีการสูญเสียพลังงานตั้งแต่ 5% ถึง 10% แต่โดยเฉลี่ยแล้วจะอยู่ที่ประมาณ 5% และเรามีเทคนิคมากมายในการหลีกเลี่ยงข้อจำกัดเหล่านี้» ให้ความมั่นใจแก่วิศวกร และเพื่อนร่วมงานของเขา Ran Berenson แบ่งปันมุมมองนี้: “ท้ายที่สุดแล้ว การกำจัดคำสั่งเก่าๆ เหล่านี้คงยากกว่าการรักษาไว้-

อ่านด้วย- Alder Lake “วิวัฒนาการที่ยิ่งใหญ่ที่สุดของ x86 ในรอบสิบปี”: Intel เผยข้อมูลภายในของโปรเซสเซอร์ Core ถัดไป(สิงหาคม 2564)

สำหรับความสัมพันธ์ที่แชมป์เปี้ยนคำสั่ง x86 มีกับ ARM และ RISC V ความจริงก็คือพวกเขามีอิทธิพลซึ่งกันและกันมาก Adi Yoaz ค่อยๆ ปฏิเสธแนวคิดของ x86 โดยเริ่มจากศูนย์ และอธิบายอย่างใจเย็นว่า “โลกของเซมิคอนดักเตอร์มีอิทธิพลซึ่งกันและกัน และรู้ว่าถ้าเรานำสถาปัตยกรรมอื่นๆ มาใช้มากมาย เราก็ได้แรงบันดาลใจจากสถาปัตยกรรมเหล่านั้นเช่นกัน เช่นเดียวกับคำสั่งที่มีขนาดคงที่ หรือสำหรับขนาดของทะเบียน โลกนี้ไม่มีใครโดดเดี่ยว”,ให้วิศวกรมั่นใจ.

เรื่องของเคมีและความร่วมมือ

เมื่อถามถึงผลกระทบของความก้าวหน้าทางเคมีและโหนดการย่อขนาดทางอุตสาหกรรมในการออกแบบลอจิกของชิป Adi Yoaz นั้นมีความชัดเจน “นี่เป็นสิ่งสำคัญอย่างยิ่ง ความสัมพันธ์ที่เรามีกับเพื่อนร่วมงานที่ทำงานด้านเคมีและวัสดุ รวมถึงเพื่อนร่วมงานในนั้นกระบวนการ (ความประณีตของการผลิต, หมายเหตุบรรณาธิการ)เป็นพื้นฐาน องค์ประกอบทั้งหมดเหล่านี้ส่งผลโดยตรงต่อการออกแบบชิป“ เขาอธิบาย

ก่อนที่จะเสริมว่าหากวิศวกรจำนวนหนึ่งมีแบบร่างของชิปอยู่ในมือ ทันทีที่งานเริ่มต้นขึ้น ขั้นตอนการทำงานก็จะถูกกระจายอย่างมหาศาล ไม่เพียงแต่ระหว่างผู้เชี่ยวชาญที่แตกต่างกัน แต่เหนือสิ่งอื่นใดระหว่างไซต์ต่างๆ ของ Intel -P-Core ''Raptor Cove'' ใหม่และการทดลองใช้ชุด SoC เสร็จสิ้นที่นี่ในอิสราเอล แต่ Intel เป็นบริษัทระดับโลกและทุกคนมีส่วนร่วม: E-Cores ได้รับการพัฒนาในออสติน(เท็กซัส)และ GPU ที่ Folsom(แคลิฟอร์เนีย)” เขาอธิบาย

Tick-Tock กลับมาแล้ว (ไม่ใช่ ไม่ใช่โซเชียลเน็ตเวิร์ก)

แม้กระทั่งก่อนที่คุณจะรับชมวิดีโอแนวตั้งบน Tik-Tok เป็นเวลาหลายชั่วโมง โลกของโปรเซสเซอร์ก็กำลังเต้นตามจังหวะของ Tick และ Tock ของ Intel ไดนามิกของการเปิดตัวโปรเซสเซอร์ซึ่งสอดคล้องกับการเปลี่ยนแปลงระหว่างการเปิดตัวสถาปัตยกรรมใหม่ (tock) และการเปลี่ยนไปสู่การแกะสลักที่ละเอียดยิ่งขึ้น (ติ๊ก) การเปลี่ยนจาก 22 นาโนเมตรเป็น 14 นาโนเมตร และการมาถึงของสถาปัตยกรรม Skylake ได้ทำลายไดนามิกนี้ด้วย "การรีเฟรช" ที่เรียบง่ายระหว่างปี 2015 ถึง 2020นับตั้งแต่เขาเข้ามาเป็นหัวหน้าของ Intel Pat Gelsinger ซีอีโอคนใหม่ของ Intel(ผู้ผลิตโปรเซสเซอร์จำนวนหนึ่งในยุค 80/90) ตัดสินใจกลับไปใช้รุ่น Tick-tock หรืออย่างน้อยก็มีความถี่ในการดำเนินการที่มากขึ้น แม้จะมุ่งมั่นให้บริษัทของเขาปรับปรุงประสิทธิภาพการแกะสลักถึงห้าครั้ง (Intel 7, Intel 4, Intel 3, Intel 20A และ Intel 18A) ในเวลาสี่ปี!

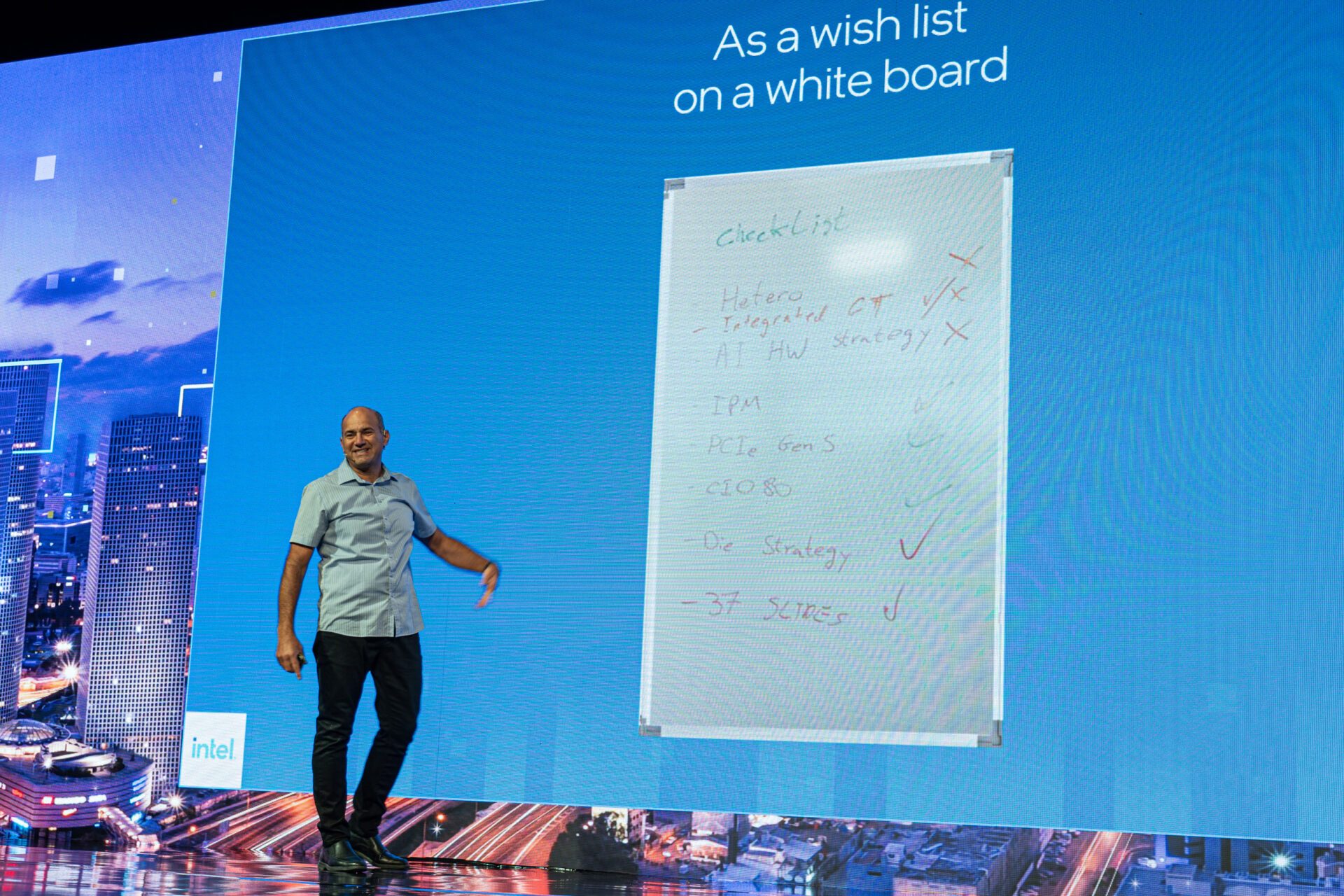

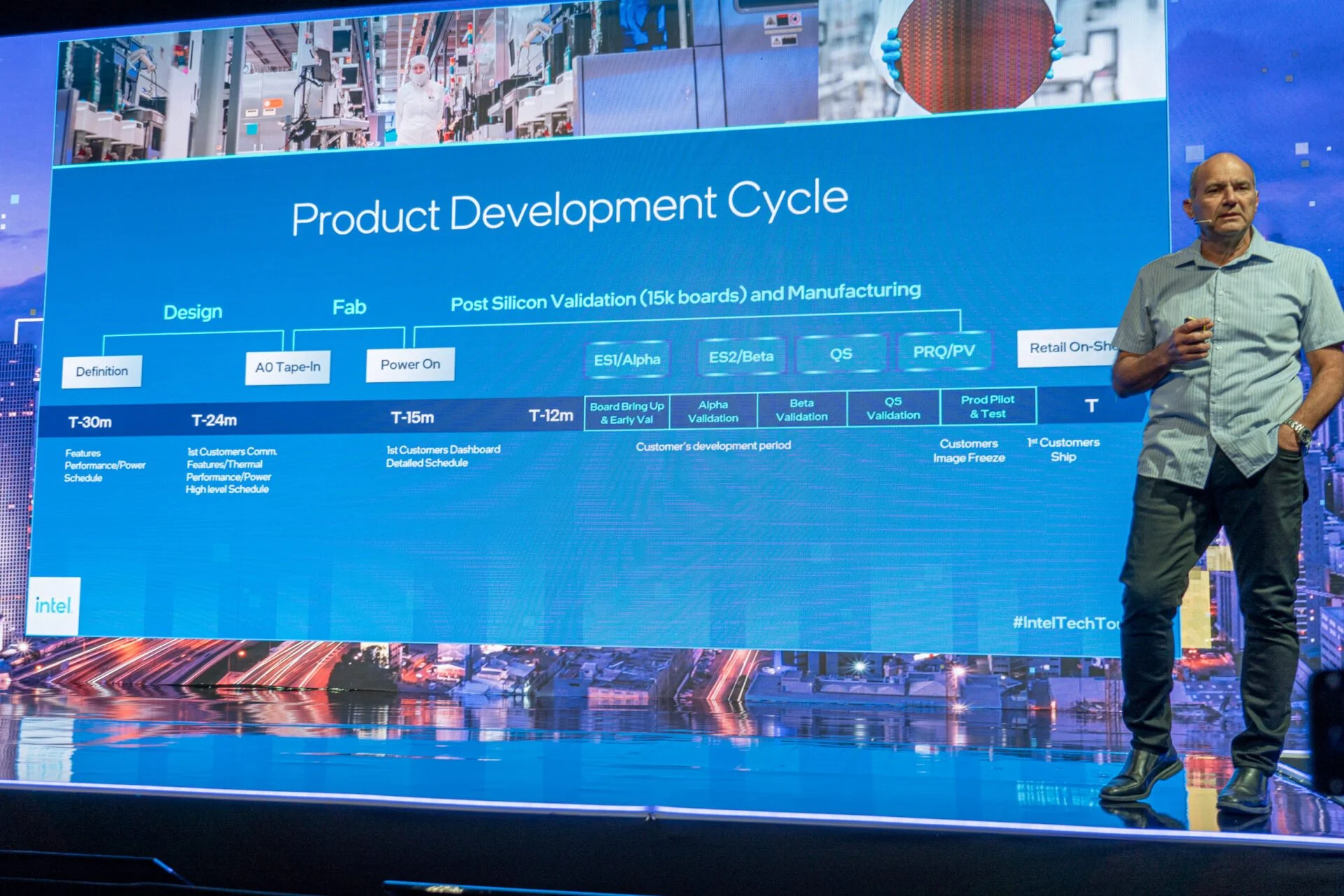

ความกดดันในการเร่งวงจรการพัฒนาอันเป็นที่รักของ Pat Gelsinger ทีมพัฒนารู้สึกได้ เพราะทั้งหมดนี้ต้องใช้เวลา -วงจรการพัฒนาผลิตภัณฑ์ใช้เวลาประมาณสามปี แต่สำหรับ Raptor Lake เราใช้เวลาเพียง 30 เดือนเท่านั้น» ภูมิใจนำเสนอไอซิก ซิลาส เขาพูดถึงเอฟเฟกต์ก้อนหิมะที่เกิดขึ้นในช่วงหกเดือนแรก: “ในตอนแรกโครงการสามารถรองรับคนได้สูงสุดสิบคน หกเดือนต่อมา มีผู้คนเข้าร่วมนับหมื่นคน!- องค์ประกอบหนึ่งที่ทำให้ Raptor Lake ทำงานได้เร็วกว่า Alder Lake มาจากพันธมิตรภายนอก: Microsoft -เมื่อเรากำหนดผลิตภัณฑ์ เราจะพูดคุยกับลูกค้าและคู่ค้าของเรา Windows 10 ไม่รองรับสถาปัตยกรรมหลักที่ต่างกัน เราได้พูดคุยกับ Microsoft ซึ่งรวมเข้ากับ Windows 11- การมาถึงของ Raptor Lake จึงสามารถเกิดขึ้นได้รวดเร็วยิ่งขึ้น

อนาคตของชิปเล็ต (และความท้าทายที่ต้องเอาชนะ)

เช่นเดียวกับ AMD ด้วย”ชิปเล็ต» เร็วๆ นี้ Intel จะประกอบ SoC ด้วยอิฐที่แตกต่างกัน ซึ่งเป็นแนวทางที่บริษัท Santa Clara เรียกการแบ่งแยก- แนวทางที่มีจุดมุ่งหมายเหนือสิ่งอื่นใดเพื่อจำกัดการเพิ่มขึ้นของราคาชิปซึ่งเชื่อมโยงกับการเพิ่มขึ้นของต้นทุนในการย่อขนาด โดยหลักการแล้ว สิ่งนี้เกี่ยวข้องกับการปรับปรุงผลผลิตโดยใช้ชิปชิ้นเล็กๆ โดยชิปขนาดใหญ่มากที่มีพื้นที่ผิว N มีค่าใช้จ่ายในการผลิตมากกว่าชิป 4 ชิ้นที่มีพื้นที่ผิวทั้งหมดเท่ากัน

อินเทลควรเปลี่ยนมาใช้เทคโนโลยีนี้เพื่อวันที่ 14จรุ่น “ทะเลสาบดาวตก”- แต่ในขณะที่นักวิเคราะห์ภายนอกรวมถึงตัวเราเอง พาร์ติชันนี้ยังคงเป็นยาครอบจักรวาล แต่ในความเป็นจริง การแยกส่วนออกเป็นชิปหลายตัวมีขีดจำกัด “ความท้าทายแรกคือการหาสมดุลที่สมบูรณ์แบบระหว่างองค์ประกอบต่างๆ” Adi Yoaz อธิบาย -สิ่งนี้ไปไกลกว่าประสิทธิภาพต่ออัตราส่วนวัตต์ เป็นอัตราส่วนประสิทธิภาพ/พลังงาน/พื้นผิว/ต้นทุนที่ซับซ้อนมากขึ้น แม้ว่าการตัดเศษจะมีประโยชน์ แต่ก็มีต้นทุนในเทคนิคการประกอบ เช่น Foveros ด้วยเช่นกัน», อธิบายวิศวกร. อย่างไรก็ตาม เขาเชื่อว่าเทคโนโลยีนี้เป็นส่วนหนึ่งของอนาคตของชิป ในลักษณะเดียวกับ “การเพิ่มตัวเร่งความเร็วไม่ว่าจะเป็นวิดีโอบล็อกเชน, การเข้ารหัส ฯลฯ -- ในบริบทที่ Intel กำลังตามล่าหาการปรับแต่งให้เหมาะสม วิศวกรของ Intel ยังพับแขนเสื้อของตนไม่เสร็จเพื่อใส่ชิปของตนมากขึ้นเรื่อยๆ เพื่อไปได้เร็วขึ้น เร็วขึ้นเสมอ

🔴 เพื่อไม่พลาดข่าวสาร 01net ติดตามเราได้ที่Google ข่าวสารetวอทส์แอพพ์-