หากค่อยๆ ดำเนินการเปลี่ยนจาก 7 นาโนเมตรเป็น 4 นาโนเมตร การเปลี่ยนจาก 4 นาโนเมตรเป็น 3 นาโนเมตรแสดงถึงความก้าวหน้าทางเทคโนโลยีที่สำคัญกว่ามาก การก้าวกระโดดที่มีทั้งความยากในทางเทคนิคและทางการเงิน แต่เหนือสิ่งอื่นใดอาจทำให้การชะลอตัวของอุตสาหกรรมที่ร้อนจัดในปัจจุบัน

ปี 2023 จะไม่ใช่ปีแห่งการแกะสลักมวล 3 นาโนเมตร หากชิป A17 ของ iPhone 15 Pro ในอนาคตนั้นอยู่ในขั้นตอนก่อนการผลิตในโรงงาน TSMC ที่เป็นความลับอย่างไม่ต้องสงสัย ก็ควรเป็นข้อยกเว้นที่พิสูจน์กฎนี้ แม้ว่า Apple จะมีกระเป๋าเงินจำนวนมากและมีพอร์ตชิปจำนวนไม่มากนัก ผู้เล่นอย่าง Qualcomm และ MediaTek ควรรออีกสักหน่อยก่อนที่จะตัดสินใจตัดสินใจ

อ่านเพิ่มเติม: TSMC ยังคงแข็งแกร่ง: 3 nm ตรงเวลาและโรงงานมูลค่า 35 พันล้านดอลลาร์(มี.ค. 2564)

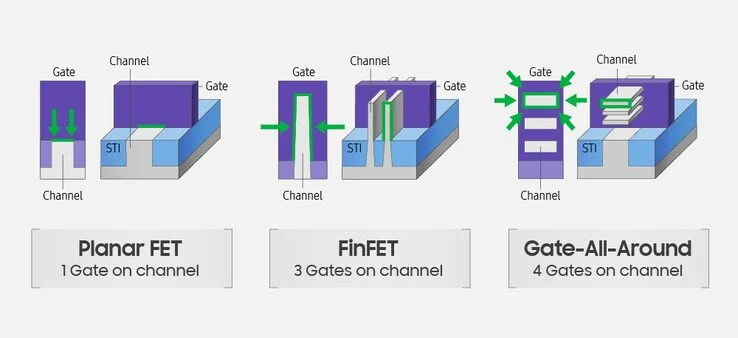

ต้องบอกว่ากระบวนการ 3 นาโนเมตร – ซึ่งเป็นพหูพจน์ที่สำคัญ – ไม่ใช่ “โหนด» (ศัพท์เฉพาะที่พูดถึงความประณีตของการแกะสลัก) ไม่เป็นอันตราย ไม่ว่าจะที่ซัมซุงที่ไหนโหนดมีพื้นฐานมาจากทรานซิสเตอร์รุ่นใหม่ หรือที่แชมป์เปี้ยน TSMC ซึ่งกระบวนการ N3 ยังคงอยู่บนทรานซิสเตอร์ FinFET แต่ที่ซึ่งการผลิตทั้งหมดได้รับการออกแบบใหม่... และจุดที่ราคาระเบิดและผลตอบแทนลดลง

กระบวนการ 3 นาโนเมตรหลายรายการ

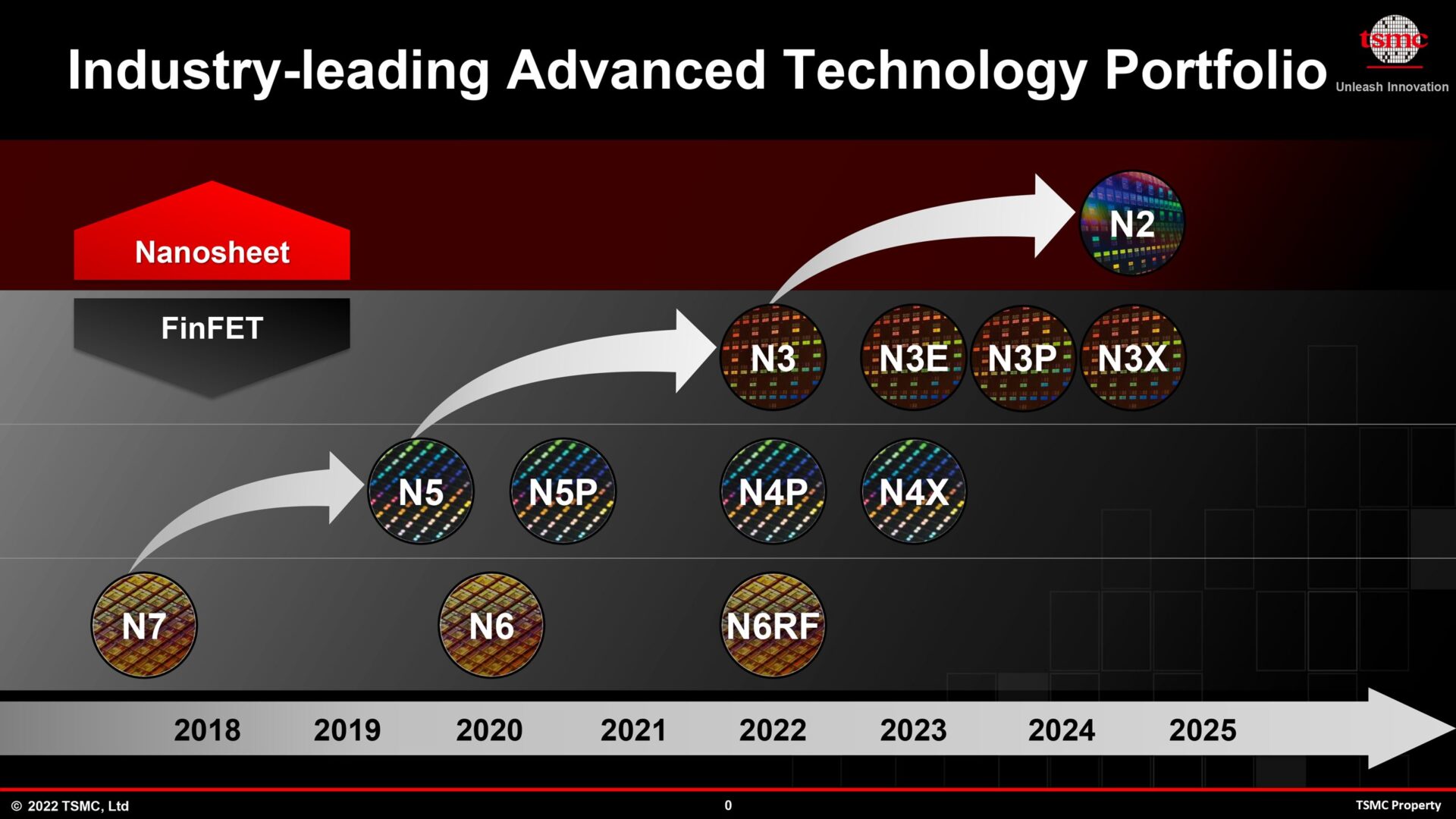

นอกเหนือจากข้อเท็จจริงที่ว่าไม่มีมาตรฐานสากลที่จะผ่านการรับรองโหนดการผลิต (ทุกคนนับนาโนเมตรในมุม) กระบวนการต่างกันในแนวทาง สำหรับ TSMC โดยที่ 6 นาโนเมตรคือส่วนขยายของ 7 นาโนเมตร และ 4 นาโนเมตรของ 5 นาโนเมตร 3 นาโนเมตรถือเป็นก้าวสำคัญจริงๆ ซึ่งต้องใช้ชิปที่ต้องแกะสลักลงไปโหนดหรือตั้งแต่เริ่มต้น ออกแบบมาเพื่อสิ่งนี้

อ่านด้วย-การย่อขนาดชิปจะไปได้ไกลแค่ไหน? Samsung สัญญาว่าจะผลิตทรานซิสเตอร์ขนาด 1.4 นาโนเมตรในปี 2570(ต.ค. 2565)

ข้อจำกัดที่มากยิ่งขึ้นคือ 3nm ของ Samsung ในขณะที่ชาวเกาหลีภาคภูมิใจที่ได้เป็นเจ้าแรกในด้านการออกแบบวงจรอันประณีตนี้ Samsung ยังได้ระบุสิ่งนี้ด้วยโหนดคงจะเป็นคนแรกที่ได้ใช้ทรานซิสเตอร์รุ่นใหม่ที่เรียกว่า “ประตูทุกรอบ" หรือกาเฟตที่ซัมซุง (แผ่นนาโนที่ ทีเอสเอ็มซี และนาโนริบบอนที่อินเทล) ทรานซิสเตอร์ใหม่เหล่านี้ประสบความสำเร็จในการใช้งาน FinFET ที่มีการใช้งานมานานกว่าทศวรรษ จึงต้องอาศัยการออกแบบที่ลึกซึ้งยิ่งขึ้น

วิธีการผลิตทั้งสองวิธีของ TSMC และ Samsung มีสิ่งนี้เหมือนกันคือใช้เครื่องพิมพ์หินอัลตราไวโอเลตสุดขีด (EUV) ที่มีชื่อเสียงอย่างหนาแน่น เครื่องจักรราคาแพงเหล่านี้ (ประมาณ 150 ล้านยูโรต่อชิ้น!) เป็นเครื่องจักรที่ประสบความสำเร็จในการนำโลกของเซมิคอนดักเตอร์ที่มีขนาดต่ำกว่า 8 นาโนเมตร ใช้สำหรับไม่กี่ขั้นตอนจาก 7 นาโนเมตร นอกเหนือจากเครื่อง DUV (อัลตราไวโอเลตลึก) แบบคลาสสิก การใช้งานจะเข้มข้นมากขึ้นเมื่อความละเอียดของการแกะสลักลดลง

ในอีกด้านหนึ่ง หากพวกเขาจำกัดจำนวนรอบของเวเฟอร์ซิลิคอนซึ่งสามารถนำไปสู่การประหยัด (ขั้นตอนน้อยลง = ข้อผิดพลาดน้อยลง = ผลผลิตที่ดีขึ้น) ความจริงที่ว่าตอนนี้มีการใช้พวกมันในทุกขั้นตอนการผลิตของชิปทำให้ราคาของเวเฟอร์(ระยะเวลาการใช้งานของแต่ละเครื่องมีอิทธิพลต่อราคาสุดท้าย) ที่เวเฟอร์เป็น "เวเฟอร์" ซิลิคอนที่มีชื่อเสียงซึ่งมีการแกะสลักวงจรของชิปในอนาคต

อัตราเงินเฟ้อราคา

ขนาดเส้นผ่านศูนย์กลาง 300 มมเวเฟอร์สิ่งที่เรียกว่า “12 นิ้ว” ที่เปิดตัวในปี 2001/2022 เป็นการรองรับชิปที่ทันสมัยที่สุด โดยยังคงมีสายการผลิตขนาด 150 มม. (6 นิ้ว) และ 200 มม. (8 นิ้ว) สำหรับชิปที่มีราคาถูกกว่า หากแผ่นเวเฟอร์ซิลิคอนมีราคาคงที่เป็นแผ่นรองรับเปล่า ราคาของมันจะแตกต่างกันอย่างมากขึ้นอยู่กับกระบวนการแกะสลักที่ใช้ในการ "เขียน" ส่วนประกอบบนพื้นผิว และโหนด3nm ได้ผลักดันราคาให้สูงกว่าในอดีตด้วยอัตราประมาณ 20,000 เหรียญสหรัฐต่อเวเฟอร์-

อ่านเพิ่มเติม: TSMC: โรงงานแกะสลัก 3 นาโนเมตรจะเปิดดำเนินการในช่วงครึ่งหลังของปี 2022(พ.ย. 2563)

หากเราเปรียบเทียบกับ 5 นาโนเมตรที่ 16,000 ดอลลาร์ และ 10,000 ดอลลาร์สำหรับ 7 นาโนเมตร ราคาจะเจ็บปวดมาก นี่เป็นเรื่องจริงโดยเฉพาะอย่างยิ่งเนื่องจากค่าใช้จ่ายเพิ่มเติม 60% ระหว่าง 5 นาโนเมตรถึง 7 นาโนเมตรยังคงทำให้สามารถเบิร์นชิปได้มากขึ้นถึง 80% (ด้วยจำนวนทรานซิสเตอร์เท่าเดิม) ในขณะที่การเปลี่ยนจาก 4/5 นาโนเมตร (กระบวนการเดียวกัน) เป็น 3 นาโนเมตรทำให้จำนวนทรานซิสเตอร์เพิ่มขึ้นเพียง 30% เท่านั้น ข้อผิดพลาดคือไม่ใช่ว่าทุกส่วนของชิปจะได้รับประโยชน์เท่ากันจากการลดขนาดวงจร – แกน CPU จะลดลงได้ง่ายกว่าหน่วยความจำ SRAM ในตัว

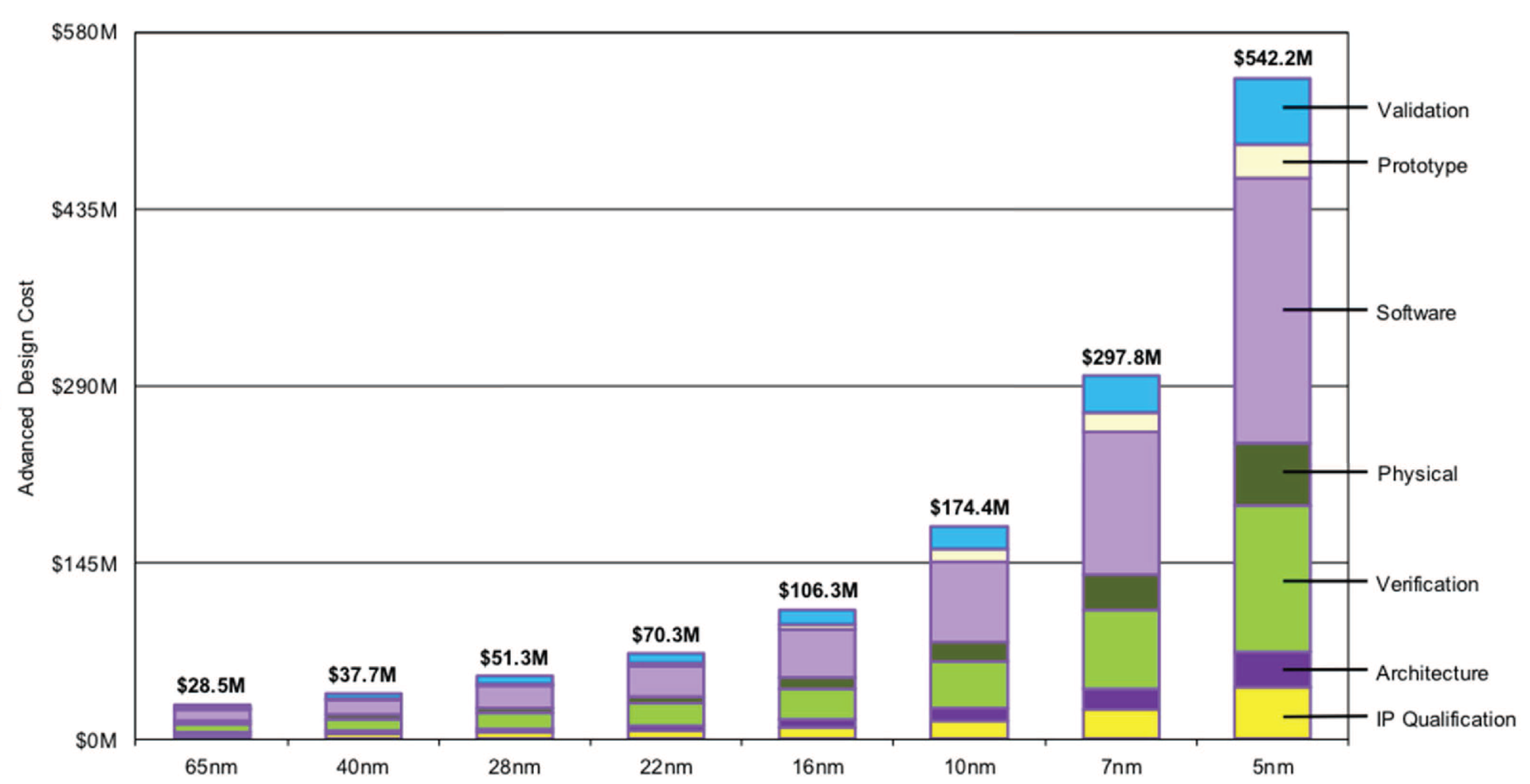

บวกกับอัตราเงินเฟ้อของราคาเวเฟอร์ไม่ใช่คนเดียวที่เจ็บ การเปลี่ยนแปลงของโหนดหรือแม้แต่การเปลี่ยนโครงสร้างของทรานซิสเตอร์ (Samsung GAAFET และแผ่นนาโนที่เทียบเท่ากับ TSMC) ล้วนเกี่ยวข้องกับค่าใช้จ่ายอื่นๆ โดยเฉพาะซอฟต์แวร์การออกแบบเซมิคอนดักเตอร์จาก Cadence และ Synopsys เครื่องมือสำคัญสำหรับการผลิตชิปเหล่านี้ห่างไกลจากเรื่องเล็ก ๆ น้อย ๆ ที่เป็นเหตุผลหนึ่ง (รวมถึงการปิดกั้นเครื่องจักร EUV จาก ASML ของเนเธอร์แลนด์) ที่ทำให้จีนไม่สามารถผลิตโปรเซสเซอร์ที่ล้ำสมัยได้

เพียงดูอัตราเงินเฟ้อในต้นทุนการออกแบบชิป: ก่อนที่คุณจะกดปุ่ม "เริ่ม» ของการผลิตภาคอุตสาหกรรม การออกแบบชิป 5 นาโนเมตรอาจมีราคาถึงครึ่งพันล้านยูโร! และมีความเสี่ยงที่จะเลวร้ายยิ่งกว่านั้นสำหรับ 3 นาโนเมตร GAAFET... ซึ่งไม่ได้หมายความว่าการผลิตจะเป็นไปไม่ได้ เพราะหากการปรับใช้สามารถชะลอลงได้ ผู้ผลิตก็จะยืนพิงกำแพง

สงครามราคาในสายตา?

ในโลกของกระบวนการผลิตขั้นสูง TSMC มีความได้เปรียบเหนือ Samsung ในความเป็นจริงแล้วชาวไต้หวันเป็นผู้ผลิตชิป 90% ที่แกะสลักที่ 7 นาโนเมตรหรือน้อยกว่า ตำแหน่งที่โดดเด่นเป็นพิเศษซึ่งผลักดันให้ชาวเกาหลีเล่นการ์ดราคาเพื่อดึงดูดลูกค้าอย่างต่อเนื่อง แต่ในขณะที่ TSMC อยู่ในสถานะที่แข็งแกร่งในช่วงที่ขาดแคลนเพื่อรักษาราคาให้อยู่ในระดับสูง แต่กระแสน้ำก็อาจพลิกผันได้ เนื่องจากความหนาแน่นที่เพิ่มขึ้นเล็กน้อยที่ 3 nm (เรียกว่า N3) นำมาเปรียบเทียบกับ 5 nm ราคา 20,000 เหรียญสหรัฐต่อเวเฟอร์จึงน่าสนใจเฉพาะในกรณีของชิปที่มีมูลค่าเพิ่มสูงมาก (มาก!)ตามที่นักวิเคราะห์สัมภาษณ์โดยเพื่อนร่วมงานของเราที่ fudzillaค่าใช้จ่ายที่สูงนี้จะจูงใจนักออกแบบชิปที่คุณรู้จัก เช่น AMD, Qualcomm, MediaTek ฯลฯ – เพื่อรอและมีสมาธิกับโหนด4 และ 5 นาโนเมตร ปล่อยให้สนามเปิดให้ Apple จ่ายราคาสูงสำหรับชิป 3 นาโนเมตร

อย่างไรก็ตาม หาก Apple เป็นลูกค้ารายใหญ่ที่มีปริมาณการผลิตสูงมาก (และมูลค่าเพิ่มสูง) การจะทำให้โรงงานทำงานเต็มกำลังการผลิตไม่เพียงพอ อย่างไรก็ตามมีโรงงานอยู่ที่นั่น ได้มีการลงทุนแล้ว และวิธีเดียวที่จะทำให้เงินลงทุนนับหมื่นล้านมีกำไรได้ก็คือทำให้มันได้ผล นี่คือเหตุผลที่นักวิเคราะห์ระบุว่า TSMC สามารถลดอัตรากำไรและลดราคาลงเพื่อดึงดูดลูกค้าได้ สิ่งนี้จะส่งผลต่อแรงกดดันต่อ Samsung ซึ่งเป็นผู้ท้าชิงในสนามให้คิดราคาต่ำที่สุดเท่าที่จะเป็นไปได้

อ่านเพิ่มเติม: IBM และ Samsung ได้พัฒนาทรานซิสเตอร์แห่งอนาคต(ธ.ค.2564)

เราสรุปได้ว่าหากอุตสาหกรรมลากเท้าเล็กน้อยสำหรับการเปิดตัว 3 นาโนเมตร ซึ่งในตอนแรกควรจะเป็นเอกสิทธิ์ของ Apple ความกดดันต่อ TSMC และ Samsung ในการสร้างผลกำไรจากการลงทุนมหาศาลน่าจะผลักดันให้พวกเขาลดราคาลงโดยเร็วที่สุด . แต่การชะลอตัวตามธรรมชาตินี้อาจส่งผลเสียต่ออนาคตของการออกแบบชิป ด้วยแผนงานสาธารณะที่หยุดที่ 2 นาโนเมตรที่ TSMC (1.8 นาโนเมตรที่ Intel สำหรับโหนดอินเทล 18) และทางผ่านของเวเฟอร์จาก 300 มม. เป็น 450 มม. เลื่อนออกไปอย่างไม่มีกำหนดเสมอ “แรงเสียดทาน” ในปัจจุบันเกิดจากโหนด3 นาโนเมตรอาจทำให้อุตสาหกรรมอยู่ระหว่างการพัฒนาช้าลงชั่วขณะหนึ่ง อุตสาหกรรมนั่นคือในบางพื้นที่ เช่น ความจำ, ความร้อนสูงเกินไป-

🔴 เพื่อไม่พลาดข่าวสาร 01net ติดตามเราได้ที่Google ข่าวสารetวอทส์แอพพ์-