ความหนาแน่นของทรานซิสเตอร์ที่เพิ่มขึ้นน้อยกว่าธรรมชาติที่เปลี่ยนแปลงสถานการณ์ การแกะสลักขนาด 2 นาโนเมตรถือเป็นครั้งแรกในประวัติศาสตร์ที่ละทิ้งทรานซิสเตอร์ FinFET และหันมาใช้ GAAFET

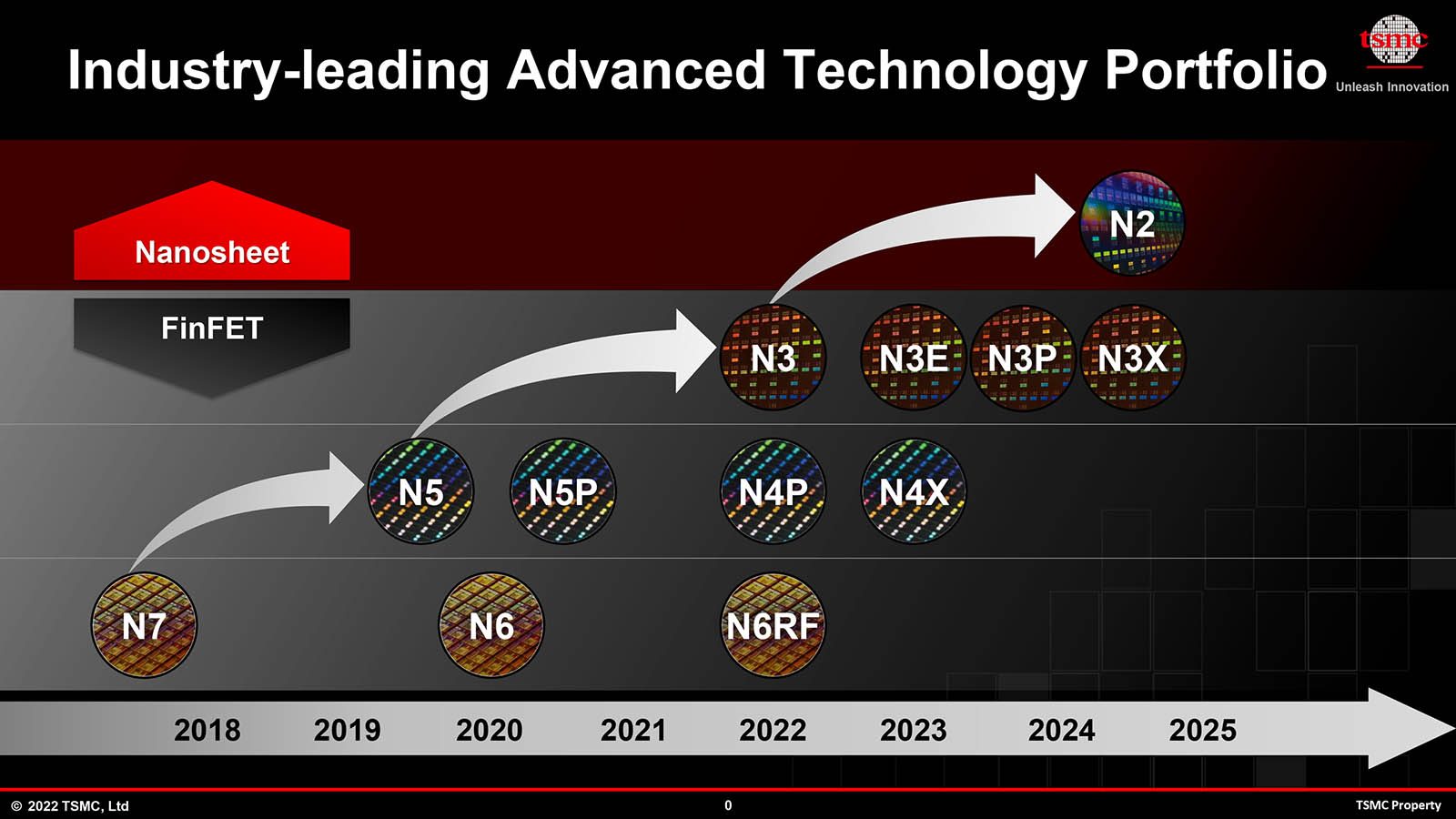

การวางแผนสำหรับปี 2025 โดยแชมป์ชิป TSMC การแกะสลักขนาด 2 นาโนเมตรถือเป็นก้าวสำคัญในการแข่งขันที่ดุเดือดในโลกของเซมิคอนดักเตอร์ แม้ว่าเราแทบจะไม่หวังที่จะไปถึง 5 นาโนเมตรเมื่อไม่กี่ปีที่ผ่านมา ไม่เพียงแต่เราจะแกะสลักที่ 4 นาโนเมตรในปี 2022 แล้วแต่นอกจากนี้โรดแมปสำหรับ 3 นาโนเมตรก็เสร็จสมบูรณ์แล้วและ 2nm กำลังเตรียมการพัฒนาอุตสาหกรรม

2 nm ที่เรียกว่า N2 จาก TSMC ของไต้หวัน ซึ่งไม่เพียงแต่คาดหวังการปรับปรุงในแง่ของการใช้พลังงานและประสิทธิภาพที่เพิ่มขึ้นเท่านั้น แต่ยังเหนือสิ่งอื่นใดคือสถาปัตยกรรมทรานซิสเตอร์ใหม่ซึ่งควรจะเป็นของทศวรรษหน้า

ประหยัดพลังงานมากขึ้น (แต่เพิ่มพลังงานปานกลาง)

การแกะสลักที่ 2 นาโนเมตรไม่ได้เพิ่มความหนาแน่นของทรานซิสเตอร์มากนัก – มากกว่า 10% เมื่อเทียบกับ 2 นาโนเมตร (N3E) – เนื่องจากลดการใช้พลังงาน อย่างมาก: การลดลงจะแกว่งไปมาระหว่าง 25 ถึง 30% เพื่อประสิทธิภาพที่เท่ากัน ถือเป็นข่าวดีอย่างเห็นได้ชัดโดยเฉพาะสมาร์ทโฟนและชิปฝังตัวทั้งหมด

ในทางกลับกัน กระบวนการนี้ช่วยให้คุณได้รับพลังงานเมื่อเทียบกับ NE3... แต่ไม่มากเท่าที่คุณจินตนาการ ใช่ บนกระดาษ การเพิ่มจาก 3 นาโนเมตรเป็น 2 นาโนเมตร ดูเหมือนว่าขนาดวงจรจะลดลง 33% หรือประหยัดพลังงานได้เกือบ 25-30% แต่ N2 ไม่ได้เพิ่มทรานซิสเตอร์อีก 33% เนื่องจากโปรเซสเซอร์ไม่เพียงแต่ประกอบด้วยส่วนที่เรียกว่า "ตรรกะ" เท่านั้น แต่ยังประกอบด้วยหน่วยความจำและองค์ประกอบแอนะล็อกอีกด้วย

และองค์ประกอบทั้งสองนี้ (SRAM และส่วนประกอบแอนะล็อกที่เกี่ยวข้องกับการควบคุมในปัจจุบัน) จะไม่ลดลงเหมือนในอดีตอีกต่อไป TSMC สื่อสารที่นี่ด้วยตัวอย่างของชิปที่ประกอบด้วยส่วนลอจิก 50% ซึ่งเป็นส่วนเดียวที่ใช้ประโยชน์จากการลดขนาดของทรานซิสเตอร์อย่างเต็มที่ แต่ยังรวมถึงหน่วยความจำ SRAM 30% และองค์ประกอบแอนะล็อก 20%

ในความเป็นจริง TSMC นับความหนาแน่นของทรานซิสเตอร์เพิ่มขึ้นเพียง 10% เมื่อเทียบกับ 3 นาโนเมตร แล้วเราจะสามารถลดการบริโภคลง 25-30% ได้อย่างไร? ขอบคุณทรานซิสเตอร์ชนิดใหม่

ลาก่อน FinFET สวัสดี GAAFET

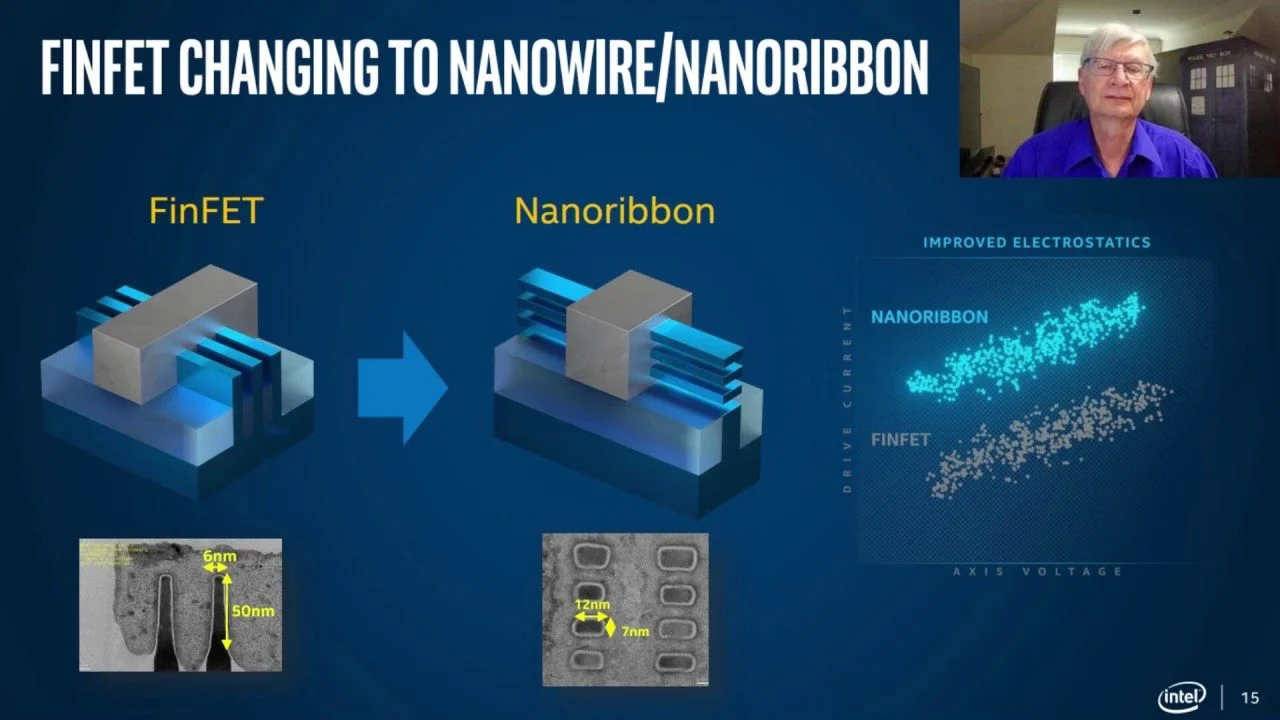

ดังที่เราได้เล่าให้ฟังไปแล้วว่าTSMC สามารถรักษาทรานซิสเตอร์ FinFET "คลาสสิก" ให้คงอยู่ได้เป็นเวลานานมาก- แต่โครงสร้างทรานซิสเตอร์แบบครีบนี้ (“fin” ในภาษาอังกฤษแปลว่า fin, fin) ได้ผ่านพ้นไปแล้ว และทรานซิสเตอร์ประเภทอื่นจะเข้ามาแทนที่ เรียกว่า nanosheet โดย TSMC, nanoribbon โดย Intel เป็นชื่อ GAAFET ของ Samsung ที่ได้รับความนิยมมากที่สุด เพราะมันอธิบายได้อย่างชัดเจนว่า “ชั้นนาโน/สายนาโน” เหล่านี้ผ่านลอจิกเกตที่ล้อมรอบพวกมันอย่างสมบูรณ์ –ประตูทรานซิสเตอร์เอฟเฟกต์สนามรอบด้าน-

และเป็นธรรมชาติของโครงสร้างนี้ที่แยกวงจรออกจากกันได้ดีขึ้นมาก ซึ่งทำให้สามารถจำกัดการใช้พลังงานได้ ความจริงที่ว่าวงจรถูกล้อมรอบอย่างสมบูรณ์ทำให้สามารถจัดการการรั่วไหลของพลังงานได้ดีขึ้น มีแรงดันไฟฟ้าละติจูดมากขึ้น เป็นต้น ปัญหาเดียวของกระบวนการนี้ที่โตชิบากำหนดไว้ในปี 1988 คือการทำให้เป็นอุตสาหกรรม และดูเหมือนว่า TSMC จะเป็นคนแรกที่ได้รับผลประโยชน์ให้กับลูกค้าในอนาคต – ใครพูดถึง Apple บ้าง?

🔴 เพื่อไม่ให้พลาดข่าวสารจาก 01net ติดตามเราได้ที่Google ข่าวสารetวอทส์แอพพ์-

แหล่งที่มา : อานันท์เทค