三星對其半導體生產部門的未來抱持著遠大的抱負。根據其五年計劃,這家韓國巨頭的目標是到 2027 年將該領域的營業額增加兩倍。

目前,三星和台積電是唯一在工業基礎上使用極紫外線雕刻的「代工廠」。但是財閥無論是在市場份額(台積電生產 90% 到 95% 的 7 奈米以下晶片!)還是在製程控制方面,該集團都遠遠落後於台積電。正是台積電的技術進步推動高通從三星(生產 Snapdragon 8 Gen 1)轉向台灣生產「Plus」版本。這也是促使 Nvidia 更喜歡台積電 (TSMC) 的 GeForce RTX 4000 採用 4 奈米製程(RTX 3000是三星刻在8nm的)。

被台積電超越後,三星不打算繼續維持這種狀態。根據蒲隆地相較之下,韓國人在 3 奈米技術上投入的資源是先前「節點」(其他等級的雕刻精度,例如 8 奈米、4 奈米等)的三倍。如果說三星是Coué方法之王,而台積電卻非常沉默,那麼韓國人似乎對自己的下一代雕刻技術充滿信心。

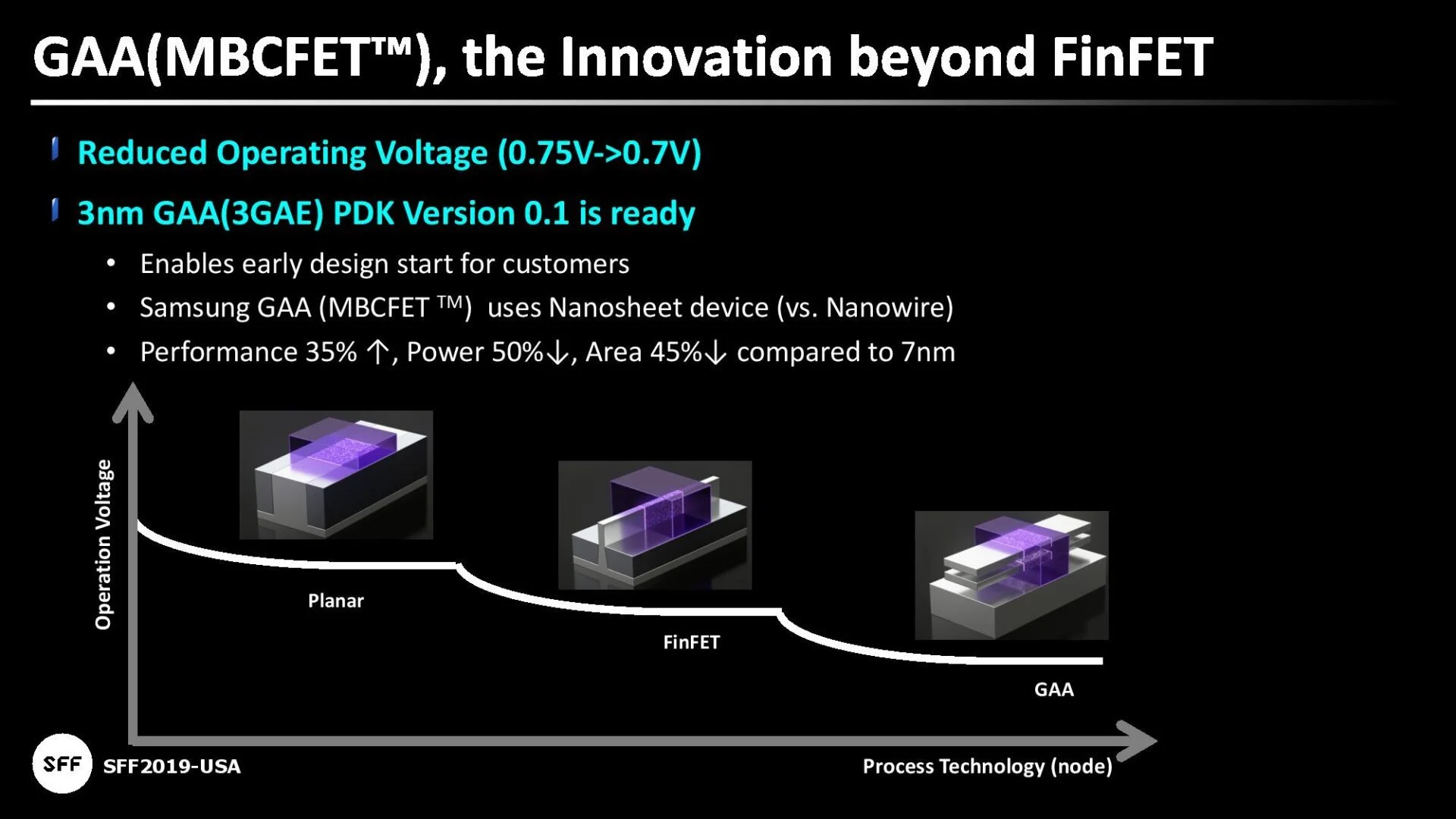

它比台積電目前使用的更有優勢。 3 nm 將是世界上第一代不採用十年來一直沿用的 FinFET 結構的電晶體,轉而採用「全能閘極」或 GAAFET 技術。三星沒有其排他性:英式積電等英特爾應該在 2024 年至 2025 年間從 2 nm 開始部署這項技術(該技術在英特爾稱為 RibbonFET/nanoribbon,在三星稱為 MBCFET)。

三星正在規劃一個與競爭對手一樣積極縮小組件尺寸的路線圖:計劃在 2024 年採用 3 nm,而 2 nm 將是對先前製程的改進,將從 2025 年開始實現工業化。

就像英特爾將自己定位在“西方半導體冠軍»,三星也打出了生產基地多元化的牌泰勒目前正在興建的工廠,靠近奧斯汀(德克薩斯州)。價值170億美元的大型工業用地!

經過數百奈米、數十奈米、幾奈米的爭奪,電晶體尺寸縮小的未來將在 2024 年開始縮小到十億分之一公尺。撞牆之前?

來源 : 蒲隆地